[아두이노] 풀다운(Pull-down), 왜 굳이 외부 저항을 써야 할까?

지난 포스팅에서 아두이노의 내부 풀업(Internal Pull-up)이 **“안에서 5V를 밀어내는 구조”**라는 것을 살펴봤습니다.

그렇다면 반대 개념인 풀다운(Pull-down)은 어떻게 동작할까요?

그리고 왜 우리는 번거롭게 외부 저항까지 추가해야 할까요?

1. 풀다운의 구조: 핀을 GND에 묶어두다

풀다운 회로는 이름 그대로 핀의 전압을 GND로 끌어내리는 구조입니다.

- 기본 연결: 핀 ↔ GND 사이에 저항 연결

- 스위치 연결: 핀 ↔ VCC(5V) 사이에 스위치 배치

즉, 평상시 핀은 저항을 통해 GND에 연결된 상태가 됩니다.

2. 작동 원리: 전압 분배(Voltage Division)의 지배

핵심은 스위치를 누를 때 발생하는 전압 분배 변화입니다.

① 스위치가 열려 있을 때 (IDLE)

아두이노 입력 핀의 내부 임피던스는 매우 큽니다.

반면 외부 풀다운 저항은 보통:

이 상태에서 핀 전압은 전압 분배 공식으로 표현하면:

즉, 핀은 사실상 GND에 붙어 있는 상태가 됩니다.

→ 내부 MOSFET은 논리값 0 (LOW) 로 인식

② 스위치를 누른 순간 (ACTIVE)

스위치를 누르면 상황이 완전히 바뀝니다.

-

위쪽(VCC): 거의

-

아래쪽(GND):

전압 분배식은 다음과 같습니다:

즉, 핀은 완전히 VCC를 따라가게 됩니다.

→ 내부 MOSFET은 논리값 1 (HIGH) 로 인식

3. 왜 내부 풀다운은 없을까?

아두이노(ATmega 계열)는 내부 풀업은 있지만 풀다운은 제공하지 않습니다.

이건 의외로 꽤 의도적인 설계입니다.

(1) 설계 단순화

모든 핀에

- 풀업

- 풀다운

두 개를 다 넣으면 회로가 복잡해집니다.

→ 하나만 제공하고 나머지는 외부에서 해결

(2) 노이즈 내성 (Noise Immunity)

디지털 회로는 전통적으로:

- GND 기준이 안정적

- 풀업 방식이 노이즈에 강함

그래서 기본값을 풀업 중심으로 설계하는 경우가 많습니다.

4. 그래도 풀다운을 쓰는 이유

풀다운의 가장 큰 장점은 직관성입니다.

- 풀다운: 누르면 → HIGH(1)

- 풀업: 누르면 → LOW(0)

사람 입장에서는:

“버튼 누르면 1이다”

이게 훨씬 자연스럽습니다.

5. 핵심 비유 (이게 진짜 중요)

풀다운 저항은 단순한 부품이 아닙니다.

핀을 ‘공중에 떠다니지 않게’ 붙잡아 두는 닻(anchor) 입니다.

입력 핀이 떠버리면 (Floating 상태):

→ 노이즈에 따라 0/1이 랜덤하게 튐

그래서 반드시 기준 전위를 만들어줘야 합니다.

6. 요약

- 풀다운은 기본적으로 0V(LOW)를 유지

- 스위치를 누르면 5V(HIGH) 로 전환

- 아두이노는 내부 풀다운이 없음 → 외부 저항 필수

- 권장 값:

7. PLC 엔지니어 관점에서 보면

이 구조는 사실 매우 익숙합니다.

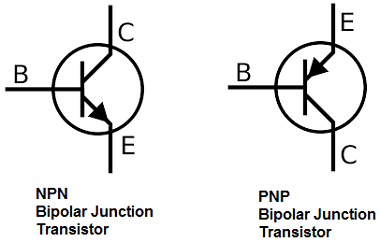

- 풀다운 = PNP(Source) 입력 구조와 유사

- “신호가 들어오면 HIGH”

PLC 경험이 있다면 오히려 풀다운이 더 직관적입니다.

마무리 한 줄

풀다운 저항은 단순한 저항이 아니라,

입력 핀을 ‘정의된 상태’로 고정하는 기준점이다.

댓글

댓글 쓰기